## 256 x 72 x 4-Bit OLED Passive Matrix Controller/Driver

PRELIMINARY DATA

(Bumped Die) **ORDER CODE: STV8105**

#### **Main Features**

- **■** Supports Monochrome OLED Passive Matrices in different formats:

- 256×72 Black & White

- 256×72×2-bits/4 levels of gray

- 256×72×4-bits/16 levels of gray

- 256×36×6-bits/64 levels of gray

- 128×72×6-bits/64 levels of gray

- On-chip DC/DC Step-up Converter

- Display Power Supply up to 25V

- Device Power Supply: 3.0 to 3.6 V

- **■** Low-power Consumption Suitable for **Battery-operated Systems**

- Column Source Current capability: 800 µA, max.

- Row Sink Current capability: 110mA, max.

- On-chip Oscillator

- Programmable Gamma Correction

- Programmable Display Multiplexing

- Two Brightness Control registers of 128 steps each

- 32 Step Dimmer Control

- One Time Programmable (OTP) fuse ROM for key configuration parameters

- Dual Scan, Master/Slave Capability

- Selectable 8-bit Parallel as well as Serial **Peripheral Interfaces**

## **Description**

The STV8105 is a low-power, controller/driver "combo" IC for OLED displays. The STV8105 supports 256 columns by 72 rows with 16 levels of gray for monochrome and 2 x 128 columns by 72 rows with 16 levels of gray for "two" color displays. It can control a display of 128 columns by 72 rows or 256 columns by 36 rows with 64 levels of gray in monochrome mode.

The STV8105 provides all necessary functions in a single chip, including on-chip supply control and bias current generators, resulting in a minimum of external components and in very low-power consumption.

The STV8105 communicates with the system via fully configurable interfaces (parallel or serial) to ease interfacing with the host microcontroller. The STV8105 has a set of command and control registers that can be addressed by these interfaces.

Rev. 1.1

1/95

## **Contents**

| Chapter 1      | General Overview                             |    |

|----------------|----------------------------------------------|----|

| 1.1            | Bumped Die Pad Description                   | 7  |

| 1.2            | Pad Signal Description                       | 12 |

| 1.3            | Lead Pad Reference Chart                     | 14 |

| 1.4            | Mechanical Dimensions                        | 15 |

| 1.5            | Functional Description                       | 16 |

| Chapter 2      | Bus Interfaces                               | 17 |

| 2.1            | Interface Sequence                           | 17 |

| 2.2            | Parallel Interface                           | 18 |

| 2.3            | Serial Interface                             | 20 |

| 2.4            | Master/Slave Connection                      | 23 |

| Chapter 3      | Display RAM                                  | 24 |

| 3.1            | 16 Level Gray Scale Mode Memory Map          | 25 |

| 3.2            | 4 Level Gray Scale Mode Memory Map           | 25 |

| 3.3            | 64 Level Gray Scale Mode 1 Memory Map        | 27 |

| 3.4            | 64 Level Gray Scale Mode 2 Memory Map        | 28 |

| 3.5            | Monochrome Mode Memory Map                   | 29 |

| 3.6            | Display RAM Loading                          | 31 |

| Chapter 4      | Dot-Matrix Display                           | 32 |

| Chapter 5      | Clock Generation                             | 34 |

| Chapter 6      | Master/Slave and Primary/Secondary Operation | 36 |

| Chapter 7      | Brightness Adjustment                        | 38 |

| Chapter 8      | DC/DC Step-up Converter with VF Detection    | 40 |

| 8.1            | General Description                          | 40 |

| 8.2            | Detailed Description                         |    |

| 8.2.1<br>8.2.2 | PWM ModePFM Mode                             |    |

| 8.3            | Compensation Network                         |    |

|                | •                                            |    |

| 8.4              | Soft Start                               | 45 |

|------------------|------------------------------------------|----|

| 8.5              | Peak Current Detection                   | 46 |

| Chapter 9        | Column Drivers                           |    |

| 9.1              | Color Selection Modes                    | 47 |

| 9.2              | Dimmer Control                           | 48 |

| 9.3              | Drive Control                            | 49 |

| 9.4              | Setup Period                             | 50 |

| 9.5              | Drive Period                             |    |

| 9.5.1<br>9.5.2   | 16 Level Gray Scale Mode                 |    |

| 9.5.2            | 64 Level Gray Scale Mode                 |    |

| 9.5.4            | Monochrome Mode                          | 57 |

| Chapter 10       | Row Driver Control                       |    |

| 10.1             | Row Drivers                              | 58 |

| 10.2             | Row Driver Scanning Modes                |    |

| 10.2.1<br>10.2.2 | Single Scanning Mode                     |    |

| 10.2.2           | Dual Scarring wode                       |    |

| Chapter 11       | OTP Memory                               |    |

| 11.1             | Introduction                             | 61 |

| 11.2             | OTP Memory Programming                   | 61 |

| 11.3             | A Short Routine for Programming the OTP  | 62 |

| Chapter 12       | STV8105 Configurations                   |    |

| 12.1             | Reset Configuration                      | 63 |

| 12.2             | Sleep Configuration                      | 63 |

| Chapter 13       | Command and Control Registers            |    |

| 13.1             | List of Commands Ordered by Command Code | 65 |

| 13.2             | Command Details Ordered by Command Code  | 67 |

| Chapter 14       | Electrical Characteristics               |    |

| 14.1             | Absolute Maximum Ratings                 | 90 |

| 14.2             | Thermal Data                             | 90 |

| 14.3             | Recommended Operating Conditions         | 90 |

| Chapter 15 | Revision History                                          |    |

|------------|-----------------------------------------------------------|----|

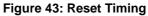

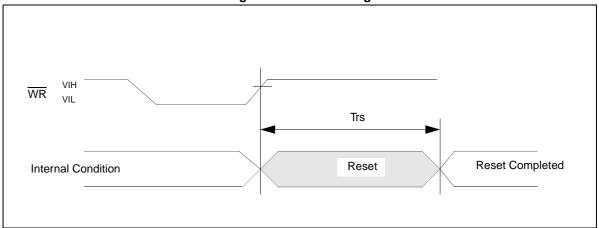

| 14.3.8     | Reset Input                                               | 93 |

| 14.3.7     | Voltage Generators                                        |    |

| 14.3.6     | DC/DC Converter                                           |    |

| 14.3.5     | Current Reference and Brightness Adjustment D/A Converter | 92 |

| 14.3.4     | Column Drivers                                            | 92 |

| 14.3.3     | Row Drivers                                               |    |

| 14.3.2     | Timing Generator                                          | 91 |

| 14.3.1     | DC Characteristics                                        | 90 |

|            |                                                           |    |

STV8105 General Overview

## 1 General Overview

The STV8105 is a monochrome, low-power controller/driver combo from STMicroelectronics' family of controllers for OLED displays. It has been developed to bring a flexible solution to applications and systems based on OLED passive matrices.

The STV8105 can be used with many different host micro-controllers. It supports a serial bus and a parallel interface covering most of the possible application architectures. This provides easy access to a set of command and control registers to properly program the STV8105.

The STV8105 includes a dual port Display RAM of 256 x 72 x 4-bits to support the full display capabilities of 256 column and 72 row drivers with several display functions.

The on-chip DC/DC step-up converter generates the necessary supply voltage (18 V, typically) for all row and column drivers from the battery.

Processed in BCD technology, the STV8105 features a low-power digital core and output drivers that can source up to  $800\,\mu\text{A}$  for columns and sink up to 110mA for rows with a display supply of up to 25 V. Thanks to the high level of integration, the number of required external components is drastically reduced.

General Overview STV8105

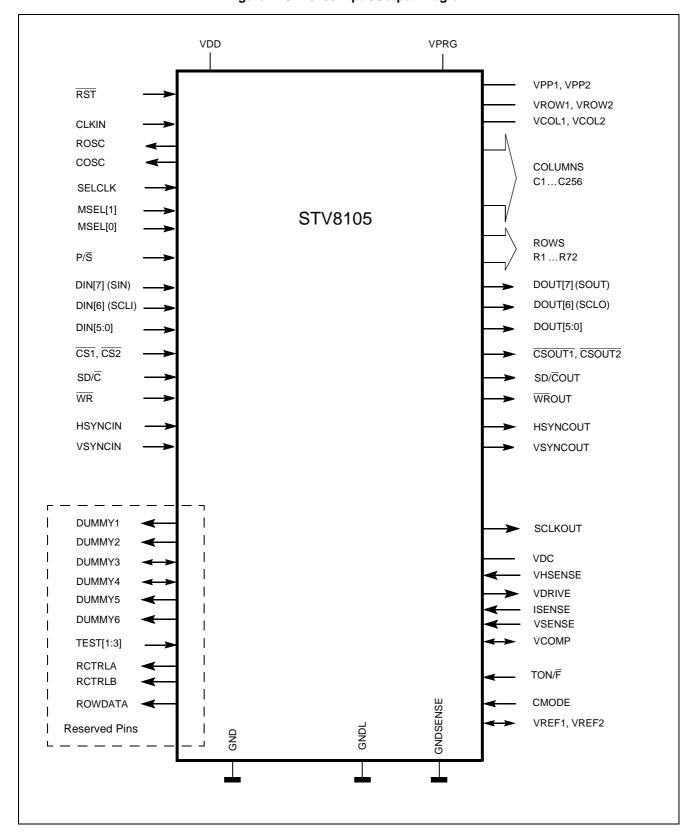

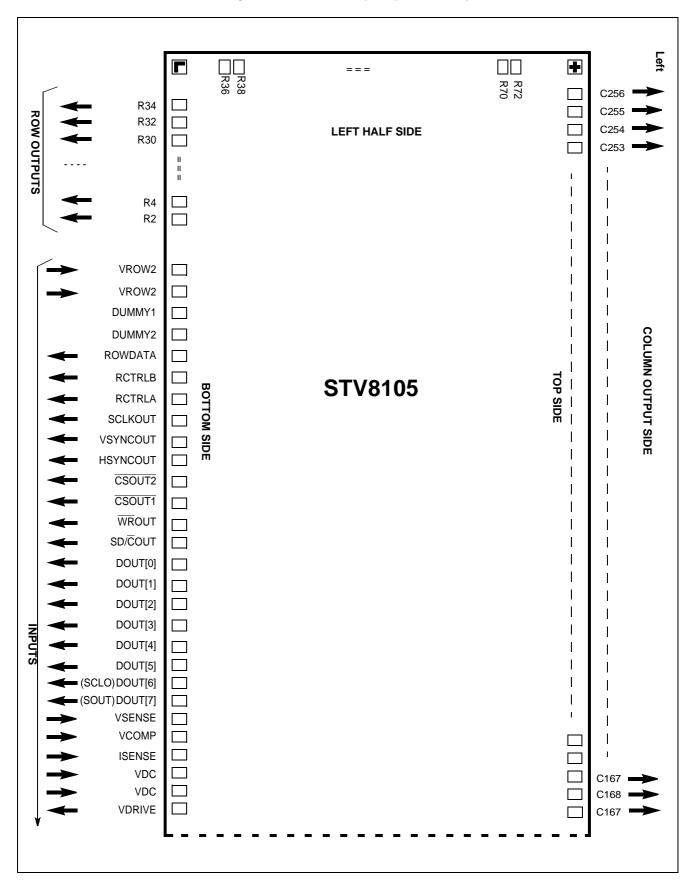

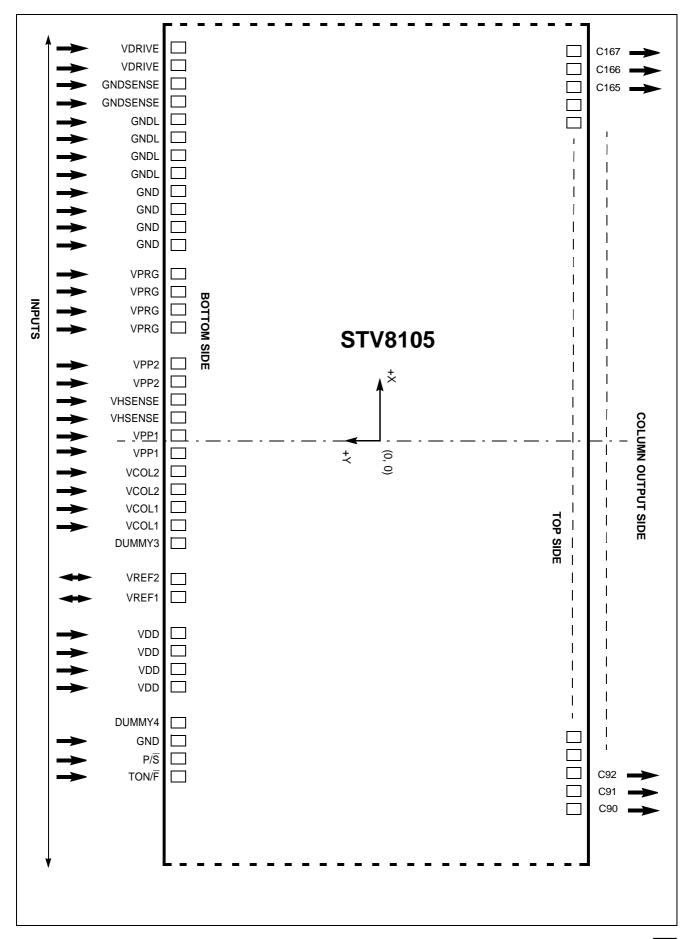

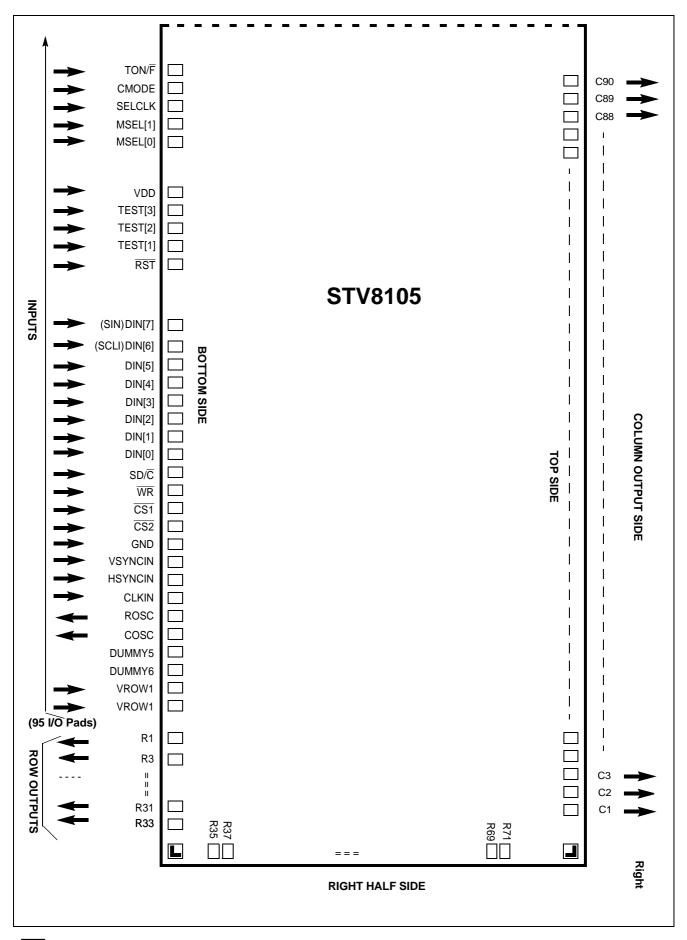

Figure 1: STV8105 Input/Output Diagram

STV8105 General Overview

## 1.1 Bumped Die Pad Description

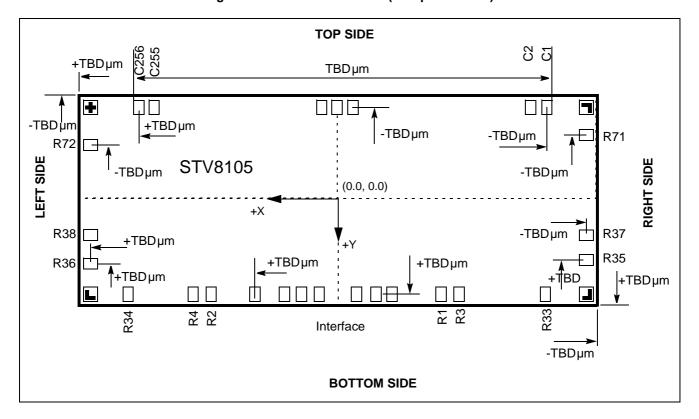

Figure 2: Die Mechanical Data (Bump-side View)

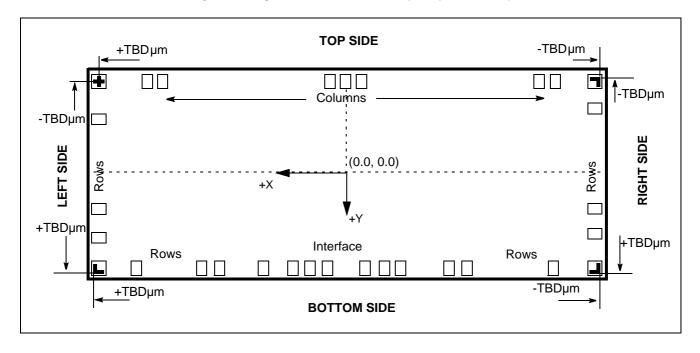

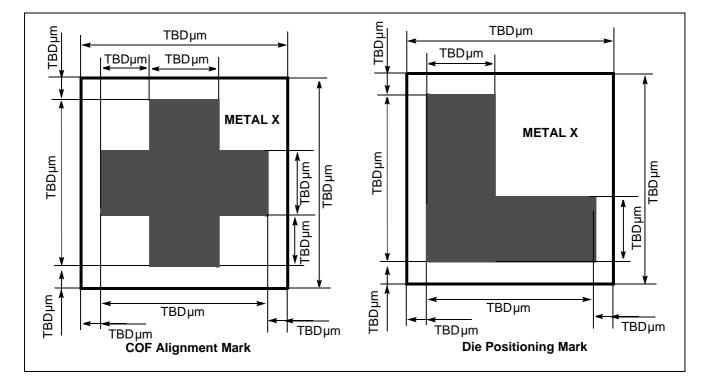

Figure 3: Alignment Mark Positions (Bump-side View)

General Overview STV8105

Figure 4: Alignment Mark Mechanical Data

STV8105 General Overview

Figure 5: Pad Position (Bump-Side View)

General Overview STV8105

STV8105 General Overview

General Overview STV8105

# 1.2 Pad Signal Description

Table 1: STV8105 Pad Description (Sheet 1 of 2)

| Ball Name      | Input/Output | Description                                                          |

|----------------|--------------|----------------------------------------------------------------------|

| C1-C256        | 0            | Column Driver Outputs                                                |

| R1-R72         | 0            | Row Driver Outputs                                                   |

| CLKIN          | 1            | External RC/Crystal connection or Clock input                        |

| CMODE          | 1            | Mode Select: "H": Dual color mode "L": Single color mode             |

| COSC           | 0            | External RC oscillator, capacitor connection                         |

| CS1            | 1            | Chip Select 1 Input (Master Device Chip Select)                      |

| CS2            | 1            | Chip Select 2 Input (Slave Device Chip Select)                       |

| CSOUT1         | 0            | Chip Select 1 Output                                                 |

| CSOUT2         | 0            | Chip Select 2 Output                                                 |

| DIN[5:0]       | 1            | P/S="H": Parallel Data Input<br>P/S="L": Not used. Fix to "H" or "L" |

| DIN[6] (SCLI)  | 1            | P/S="H": Parallel Data Input P/S="L": Serial Clock Input             |

| DIN[7] (SIN)   | 1            | P/S="H": Parallel Data Input<br>P/S="L": Serial Data Input           |

| DOUT[5:0]      | 0            | $P/\overline{S}$ ="H": Parallel Data Output P/S="L": Non Connection  |

| DOUT[6] (SCLO) | 0            | P/S="H": Parallel Data Output<br>P/S="L": Serial Clock Output        |

| DOUT[7] (SOUT) | 0            | P/S="H": Parallel Data Output<br>P/S="L": Serial Data Output         |

| GND            | Supply       | Analog and Digital ground                                            |

| GNDL           | Supply       | Column and Row driver ground                                         |

| GNDSENSE       | Supply       | Ground for DC/DC Converter                                           |

| HSYNCIN        | 1            | Horizontal SYNC Input                                                |

| HSYNCOUT       | 0            | Horizontal SYNC Output                                               |

| ISENSE         | 1            | Over current sense signal for external switching MOS transistor      |

| MSEL[0]        | I            | Master /Slave Select: "H": Master "L": Slave                         |

| MSEL[1]        | I            | Primary /Secondary Select: "H": Primary "L": Secondary               |

| P/S            | 1            | Parallel Interface or Serial Interface Select                        |

| RCTRLA         | 0            | Reserved for Test                                                    |

| RCTRLB         | 0            | Reserved for Test                                                    |

| ROSC           | 0            | External RC oscillator, resistor connection or Crystal connection    |

STV8105 General Overview

Table 1: STV8105 Pad Description (Sheet 2 of 2)

| Ball Name    | Input/Output | Description                                                                                                     |

|--------------|--------------|-----------------------------------------------------------------------------------------------------------------|

| ROWDATA      | 0            | Reserved for Test                                                                                               |

| RST          | I            | System Reset Input                                                                                              |

| SCLKOUT      | 0            | System Clock Output                                                                                             |

| SD/C         | I            | Display Data or Command: SD/C="H": Display Data SD/C="L": Command                                               |

| SD/COUT      | 0            | SD/C Output                                                                                                     |

| SELCLK       | I            | "H": An internal oscillator (if MSEL[0]="1") "L": External clock used                                           |

| TEST[2:1]    | I            | Test Mode Select: "H": Test Mode OFF (internal pull-up) "L": Reserved modes                                     |

| TEST[3]      | I            | Reserved (internal pull-up)                                                                                     |

| TON/F        | I            | DC/DC Converter Mode Select  "H": PFM constant t <sub>ON</sub> mode  "L": PWM constant switching frequency mode |

| VCOL1        | Supply       | Odd column supply                                                                                               |

| VCOL2        | Supply       | Even column supply                                                                                              |

| VCOMP        | I/O          | Compensation pad for DC/DC converter, constant frequency PWM mode                                               |

| VDC          | Supply       | Supply for gate drive output buffer                                                                             |

| VDD          | Supply       | Analog/Digital low-voltage controller supply                                                                    |

| VDRIVE       | 0            | Gate drive for external switching MOS transistor                                                                |

| VHSENSE      | I            | VH sense input                                                                                                  |

| VPP1         | Supply       | Odd column driver power supply                                                                                  |

| VPP2         | Supply       | Even column driver power supply                                                                                 |

| VPRG         | Supply       | Non-volatile OTP memory program power supply                                                                    |

| VREF1        | I/O          | Reference Voltage 1                                                                                             |

| VREF2        | I/O          | Reference Voltage 2                                                                                             |

| VROW1        | Supply       | Odd row driver supply                                                                                           |

| VROW2        | Supply       | Even row driver supply                                                                                          |

| VSENSE       | I            | Feedback signal                                                                                                 |

| VSYNCIN      | I            | Vertical SYNC Input                                                                                             |

| VSYNCOUT     | 0            | Vertical SYNC Output                                                                                            |

| WR           | I            | Display Data and Command Write Pulse                                                                            |

| WROUT        | 0            | Write Pulse Output                                                                                              |

| DUMMY1,2,5,6 | 0            | Reserved for Test                                                                                               |

| DUMMY3,4     | I/O          | Reserved for Test                                                                                               |

General Overview STV8105

## 1.3 Lead Pad Reference Chart

The reference for the following tables is the center of the die (X = 0.0, Y = 0.0)

Table 2: Top Side (from left to right)

| Lead Pad Name | Pad Placemen | ts (center), µm | Pad Dimer | nsions, µm |

|---------------|--------------|-----------------|-----------|------------|

| Leau Fau Name | Х            | Υ               | Х         | Υ          |

| C256          | TBD          | TBD             | TBD       | TBD        |

|               |              |                 |           |            |

| C2            | TBD          | TBD             | TBD       | TBD        |

| C1            | TBD          | TBD             | TBD       | TBD        |

Table 3: Right Side (from top to bottom)

| Lead Pad Name | Pad Plac | cements | Pad Dimensions |     |  |

|---------------|----------|---------|----------------|-----|--|

| Leau Fau Name | Х        | Y       | Х              | Y   |  |

| R71           | TBD      | TBD     | TBD            | TBD |  |

|               |          |         |                |     |  |

| R37           | TBD      | TBD     | TBD            | TBD |  |

| R35           | TBD      | TBD     | TBD            | TBD |  |

Table 4: Bottom Side (from right to left)

| Lead Pad Name | Pad Plac | cements | Pad Dim | ensions |

|---------------|----------|---------|---------|---------|

| Lead Pad Name | Х        | Υ       | Х       | Υ       |

| R33           | TBD      | TBD     | TBD     | TBD     |

|               |          |         |         |         |

| R1            |          |         |         |         |

| VROW1         |          |         |         |         |

|               |          |         |         |         |

|               |          |         |         |         |

| VROW2         |          |         |         |         |

| R2            |          |         |         |         |

|               |          |         |         |         |

| R34           |          |         |         |         |

STV8105 General Overview

Table 5: Left Side (from bottom to top)

| Lead Pad Name | Pad Placements |     | Pad Dimensions |     |

|---------------|----------------|-----|----------------|-----|

| Leau Fau Name | Х              | Υ   | Х              | Υ   |

| R36           | TBD            | TBD | TBD            | TBD |

| R38           | TBD            | TBD | TBD            | TBD |

|               |                |     |                |     |

| R72           | TBD            | TBD | TBD            | TBD |

## 1.4 Mechanical Dimensions

**Table 6: Mechanical Dimensions**

| Description          | Dimension          |

|----------------------|--------------------|

| Die Size (mm x mm)   | 12.5 x 1.72        |

| Pad Pitch (μm)       | 45 - 80            |

| Pad Size (μm)        | TBD                |

| Pad Height (μm)      | 20                 |

| Wafer Thickness (µm) | 450                |

| Bump Size (μm)       | 46 x 66 and13 x 66 |

| Bump Characteristics | gold, electrolytic |

| Bump Hardness        | 30-80Hv            |

General Overview STV8105

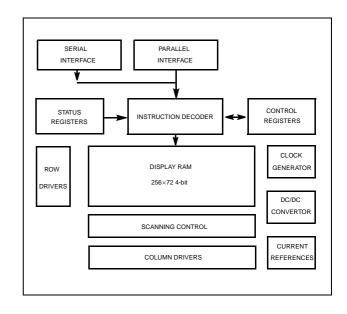

#### 1.5 Functional Description

The architecture of the STV8105 provides all of the functions required to drive OLED displays. The block diagram below gives an overview of the different on-chip components, embedded functions and their links.

**SERIAL PARALLEL INTERFACE INTERFACE** CONTROL **STATUS** INSTRUCTION DECODER **REGISTERS REGISTERS** CLOCK **DISPLAY RAM GENERATOR ROW DRIVERS** 256×72 4-bit DC/DC **CONVERTER SCANNING CONTROL CURRENT COLUMN DRIVERS REFERENCES**

Figure 6: STV8105 Block Diagram

The following rules are used in this datasheet to describe bit, bit-fields and registers:

- ROWDRVSEL is the name of a register,

- RDIR.ROWDRVSEL is the RDIR bit of register ROWDRVSEL,

- RMODE.ROWDRVSEL is the RMODE bit-field of register ROWDRVSEL.

Refer to Chapter 13: Command and Control Registers on page 64 for details of the various registers.

The various functions of the STV8105 are described in the following sections, starting with the bus interfaces.

STV8105 Bus Interfaces

## 2 Bus Interfaces

The parallel interface and serial interface are selected using a P/S pad.

The parallel interface is active when  $P/\overline{S} = "H"$ ; the serial interface when  $P/\overline{S} = "L"$ .

The serial input pads SIN and SCLI are shared with DIN7 and DIN6, respectively.

Buffered versions of the serial signals, for cascading purposes, are output on pads SOUT and SCLO and shared with DOUT7 and DOUT6, respectively.

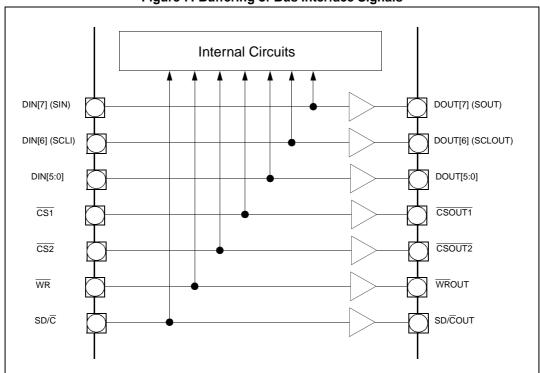

The parallel interface pads DIN[7:0],  $\overline{CS1}$ ,  $\overline{CS2}$  and  $\overline{WR}$  are buffered and sent out on DOUT[7:0],  $\overline{CSOUT1}$ ,  $\overline{CSOUT2}$ , and  $\overline{WROUT}$ .

CS1 and CSOUT1 are chip select signals for the Primary-Master and Secondary-Master devices.

CS2 and CSOUT2 are chip select signals for the Primary-Slave and Secondary-Slave devices.

Figure 7: Buffering of Bus Interface Signals

## 2.1 Interface Sequence

After Reset or Power ON, an interface is in the state of waiting for a Command Address and Display RAM Data.

After receiving the Command Address, the interface is in the state of waiting for Command Data.

When Command Data is received while in the receive Command Data state, the interface returns to the receive Command Address state.

When Display RAM Data is received while in the receive Command Data state, the interface also returns to the receive Command Address state.

Bus Interfaces STV8105

When the Serial Interface is selected, the output buffer for the interface signals is cleared when  $\overline{\text{CS1}}$  and  $\overline{\text{CS2}}$  are both "High".

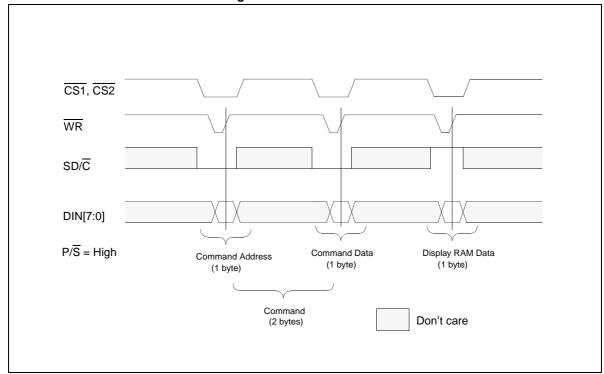

#### 2.2 Parallel Interface

The parallel interface is active when pad  $P/\overline{S}$  is "High".

When writing parallel data, the  $\overline{WR}$  pad is asserted while  $\overline{CS1}$  and  $\overline{CS2}$  are both "Low".

Data is interpreted as a command if  $SD/\overline{C}$  is "Low"; it is interpreted as Display RAM data if  $SD/\overline{C}$  is "High".

When transmitting a command, the command address is sent first followed by command data.

A command is decided by a 2-byte access: a command code followed by a data byte.

When there is a Display RAM access with  $SD/\overline{C}$  set "High" but without respecting the "2-byte nature" of a command, the STV8105 enters the state where it is waiting for a Command Address.

Figure 8: Parallel Interface

STV8105 Bus Interfaces

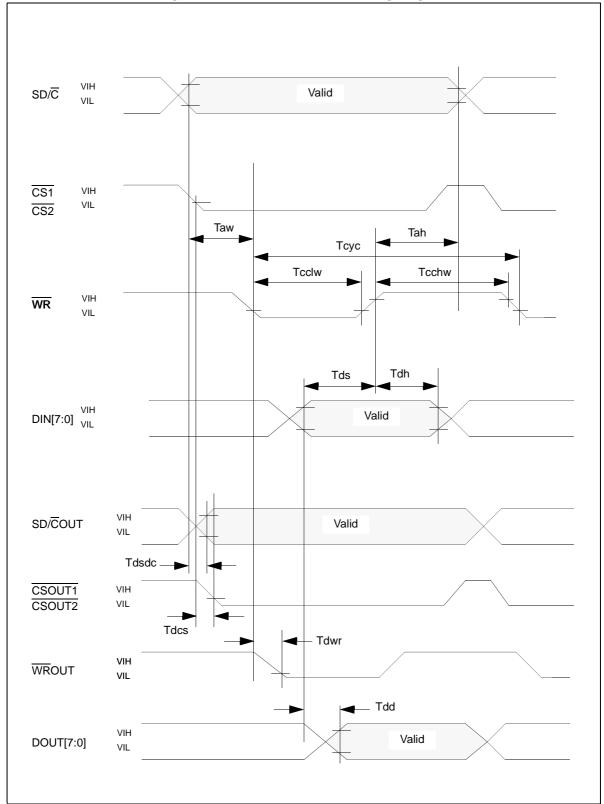

Figure 9: 8-bit Parallel Interface Timing Diagram

Bus Interfaces STV8105

**Table 7: 8-bit Parallel Interface Timing**

| Symbol | Parameter          | Test Conditions | Min. | Тур. | Max. | Units |

|--------|--------------------|-----------------|------|------|------|-------|

| Tah    | Address Hold Time  | WR              | 10   |      |      | ns    |

| Taw    | Address Setup Time | WR              | 0    |      |      | ns    |

| Тсус   | System Cycle Time  | CS1, CS2        | 200  |      |      | ns    |

| Tcclw  | Write Pulse Width  | WR              | 60   |      |      | ns    |

| Tds    | Data Setup Time    | DIN[7:0]        | 60   |      |      | ns    |

| Tdh    | Data Hold Time     | DIN7:0]         | 10   |      |      | ns    |

| Tdsdc  | SD/C Output Delay  | SD/COUT         |      |      | 30   | ns    |

| Tdcs   | CS Output Delay    | CSOUT1, CSOUT2  |      |      | 30   | ns    |

| Tdwr   | WR Output Delay    | WROUT           |      |      | 30   | ns    |

| Tdd    | DATA Output        | DOUT[7:0]       |      |      | 30   | ns    |

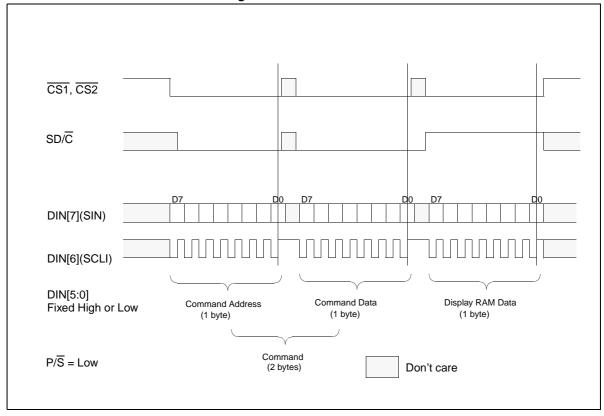

#### 2.3 Serial Interface

The serial interface is active when  $P/\overline{S}$  is "Low".

Serial data is written in using DIN[7] (SIN) and DIN[6] (SCLI) while  $\overline{\text{CS1}}$  and  $\overline{\text{CS2}}$  are both "Low".

Data is interpreted as a command if  $SD/\overline{C}$  is "Low"; it is interpreted as Display RAM data if  $SD/\overline{C}$  is "High".

DIN[5:0] are not used; they should be tied either "High" or "Low".

STV8105 Bus Interfaces

Figure 10: Serial Interface

Bus Interfaces STV8105

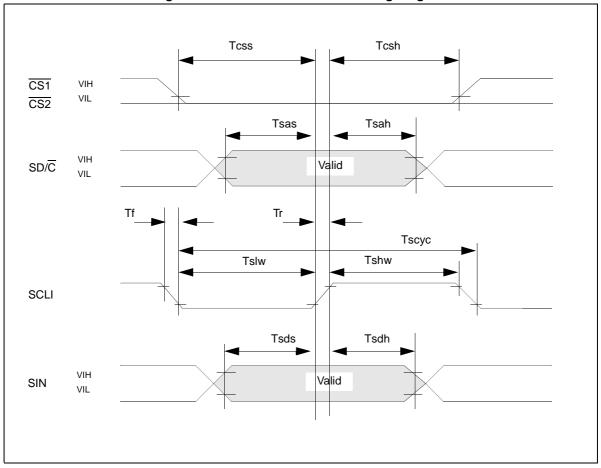

Figure 11: 4-wire Serial Interface Timing Diagram

**Table 8: 4-wire Serial Interface Timing**

| Symbol | Parameter          | Test Conditions | Min. | Тур. | Max. | Units |

|--------|--------------------|-----------------|------|------|------|-------|

| Tscys  | Serial Clock Cycle |                 | 200  |      |      | ns    |

| Tshw   | Pulse Width (High) |                 | 90   |      |      | ns    |

| Tslw   | Pulse Width (Low)  |                 | 90   |      |      | ns    |

| Tsas   | Address Setup Time |                 | 20   |      |      | ns    |

| Tsah   | Address Hold Time  |                 | 20   |      |      | ns    |

| Tsds   | Data Setup Time    |                 | 20   |      |      | ns    |

| Tsdh   | Data Hold Time     |                 | 20   |      |      | ns    |

| Tcss   | CS-SCL Time        |                 | 20   |      |      | ns    |

| Tcsh   | CS-SCL Time        |                 | 20   |      |      | ns    |

STV8105 Bus Interfaces

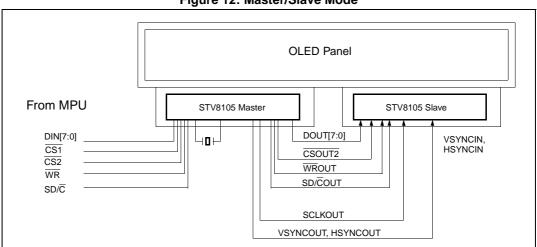

#### 2.4 Master/Slave Connection

Figure 12 below shows an example connection between two STV8105 ICs for Master/Slave mode.

Figure 12: Master/Slave Mode

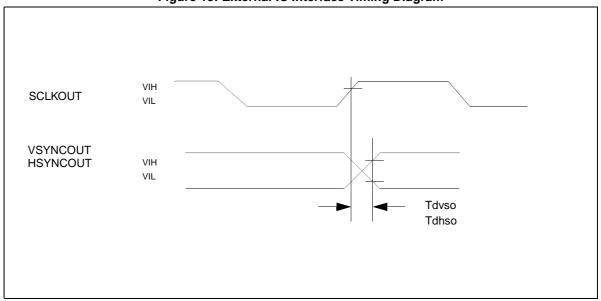

Figure 13: External IC Interface Timing Diagram

**Table 9: External IC Interface Timing**

| Symbol | Parameter      | Test Conditions | Min. | Тур. | Max. | Units |

|--------|----------------|-----------------|------|------|------|-------|

| Tdvso  | VSYNCOUT Delay |                 |      |      | 20   | ns    |

| Tdhso  | HSYNCOUT Delay |                 |      |      | 20   | ns    |

Display RAM STV8105

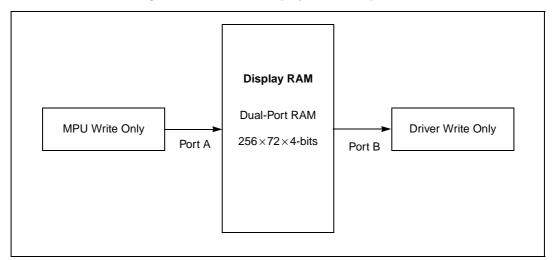

## 3 Display RAM

The STV8105 contains a Dual Port,  $256 \times 72 \times 4$ -bit Display RAM. As shown in Figure 14 below, Port A is for write only; Port B, read only.

It is possible to access any location thanks to X and Y, programmable pointers with ranges corresponding to the selected display mode.

The X address is specified with the command RAMXSTART, the Y address with RAMYSTART.

The X and Y addresses can be automatically incremented with bits YINC and XINC of the GSADDINC command. The GSMODE bit-field of this command is also used to select the display mode and gray scale. See Section 13.2 for details.

Depending on the selected display mode, one, two or four pictures can be stored in the Display RAM, and one or two colors can be controlled:

16 level gray scale mode: 256 × 72 × 4 bits - 1 picture - one/two colors

4 level gray scale mode: 256 × 72 × 2 bits - 2 pictures - one/two colors

64 level gray scale mode 1:  $128 \times 72 \times 6$  bits - 1 picture - one color

64 level gray scale mode 2:  $256 \times 36 \times 6$  bits - 1 picture - one color

Black and White, monochrome mode:  $256 \times 72 \times 1$  bit - 4 pictures - one/two colors

Figure 14: Dual Port Display RAM Composition

STV8105 Display RAM

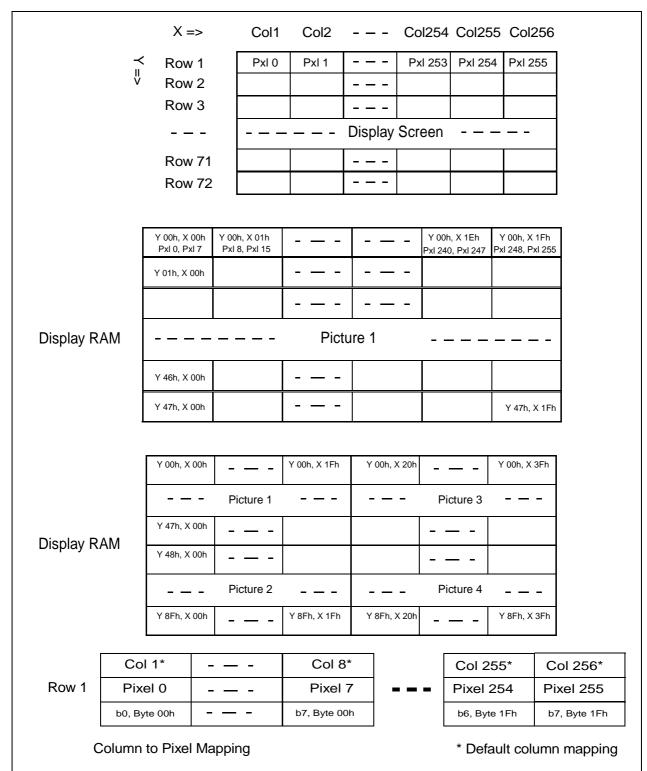

#### 3.1 16 Level Gray Scale Mode Memory Map

In this mode, the picture has 256 x 72 pixels, and the gray scale of each pixel is defined by the corresponding 4-bit value stored in Display RAM. This mode is selected using field GSMODE of the GSADDINC command. Only one picture can be stored in the Display RAM. The range of the address pointers is 00h to 7Fh for X and 00h to 47h for Y. One byte loaded in Display RAM contains data for two pixels. See Section 13.2 for details. The "two" color mode can be used; see Section 9.1: Color Selection Modes for details.

X => Col1 Col2 Col254 Col255 Col256 Row 1 PxI 0 Pxl 1 - - -Pxl 253 Pxl 254 Pxl 255 Row 2 Row 3 - - -Display Screen **Row 71 Row 72** Y 00h, X 00h Y 00h, X 01h Y 00h, X 7Dh Y 00h, X 7Eh Y 00h, X 7Fh Pxl 0, Pxl 1 Pxl 2, Pxl 3 Pxl 250, Pxl 251 Pxl 254, Pxl 255 Pxl 252, Pxl 253 Y 01h, X 00h Display RAM Y 46h, X 00h Y 47h, X 00h Y 47h, X 7Fh Col 1\* Col 2\* Col 3\* Col 255\* Col 256\* Row 1 Pixel 0 Pixel 2 Pixel 1 Pixel 254 Pixel 255 b3---b0, Byte 00h b7---b4, Byte 00h b3---b0, Byte 01h b3---b0, Byte 7Fh b7---b4, Byte 7Fh Column to Pixel Mapping \* Default column mapping

Figure 15: 16 Level Gray Scale Mode - Display RAM Organization

#### 3.2 4 Level Gray Scale Mode Memory Map

In this mode, the picture has 256 x 72 pixels. The gray scale of each pixel is defined by the corresponding 2-bit value stored in Display RAM. This mode is selected using field GSMODE of the GSADDINC command. Two pictures can be stored in the Display RAM. The range of the address pointers is 00h to 3Fh for X and 00h to 8Fh for Y. One byte loaded in Display RAM contains data for 4 pixels. See Figure 16 for details. The "two" color mode can be used, see Section 9.1: Color Selection Modes for details.

Display RAM STV8105

Figure 16: 4 Level Gray Scale Mode - Display RAM Organization

|                         |                | X =>                    | Col1 Co              | ol2    |                          | Col254  | Col25                 | 5 Col256                         | <u> </u>       |

|-------------------------|----------------|-------------------------|----------------------|--------|--------------------------|---------|-----------------------|----------------------------------|----------------|

|                         |                |                         | Pxl 0 Px             |        |                          | Pxl 253 |                       |                                  | ,<br>]         |

|                         | ,              | ≺ Row 1<br>∥<br>V Row 2 | PXIO PX              | .1 1   |                          | FXI 200 | FXI 25                | 4 FXI 255                        | _              |

|                         |                | Row 3                   |                      |        |                          |         |                       |                                  | _              |

|                         |                |                         |                      |        | Display                  | Screen  |                       |                                  | _              |

|                         |                | Row 71                  |                      |        |                          |         |                       |                                  |                |

|                         |                | Row 72                  |                      |        |                          |         |                       |                                  |                |

|                         |                |                         |                      |        |                          |         |                       |                                  |                |

|                         |                |                         | h, X 01h<br>4, Pxl 7 |        | <b>-</b> -               |         | , X 3Eh<br>3, Pxl 251 | Y 00h, X 3Fh<br>Pxl 252, Pxl 255 | 5              |

|                         |                | Y 01h, X 00h            |                      |        |                          | -       |                       |                                  | 1              |

|                         |                |                         | <u> </u>             |        |                          | _       |                       |                                  | 1              |

|                         |                |                         |                      | D: -4. | 1                        |         |                       |                                  | _              |

| Display RAM             |                |                         | <br>                 | Pictu  | ure 1                    |         |                       |                                  |                |

|                         |                | Y 46h, X 00h            |                      |        | - —                      | -       |                       |                                  |                |

|                         |                | Y 47h, X 00h            |                      |        |                          | -       |                       | Y 47h, X 3Fh                     | ו              |

|                         |                |                         | h, X 01h<br>4, Pxl 7 |        |                          |         | , X 3Eh<br>3, Pxl 251 | Y 48h, X 3Fh<br>Pxl 252, Pxl 255 | 5              |

|                         |                | Y 49h, X 00h            |                      |        |                          | -       |                       |                                  | 1              |

|                         |                |                         |                      |        | <u> </u>                 | -       |                       |                                  | 1              |

|                         |                | Picture 2               |                      |        |                          |         |                       |                                  |                |

|                         |                |                         |                      | 1 1010 | T                        |         |                       |                                  | _              |

|                         |                | Y 8Eh, X 00h            |                      |        |                          | -       |                       |                                  | _              |

|                         |                | Y 8Fh, X 00h            |                      |        |                          | -       |                       | Y 8Fh, X 3Fh                     | n              |

|                         |                |                         |                      |        |                          |         |                       |                                  |                |

|                         |                |                         |                      |        |                          |         |                       |                                  |                |

|                         |                |                         |                      |        |                          |         |                       |                                  |                |

|                         | Col 1*         | Col 2*                  | Col 3*               |        | Col 4*                   |         | Co                    | l 255*                           | Col 256*       |

| Row 1                   | Pixel 0        | Pixel 1                 | Pixel 2              |        | Pixel 3                  |         | - Pix                 | el 254                           | Pixel 255      |

|                         | b1b0, Byte 00h | b3b2, Byte 00h          | b5b4, Byte 00h       | b7     | -b6, Byte 0              | 0h      | b5b                   | 4, Byte 7Fh                      | b7b6, Byte 7Fh |

| Column to Pixel Mapping |                |                         |                      |        | * Default column mapping |         |                       |                                  |                |

STV8105 Display RAM

## 3.3 64 Level Gray Scale Mode 1 Memory Map

In this mode, the picture has 128 x 72 pixels. The gray scale of each pixel is defined by the corresponding 6-bit value stored in Display RAM. This mode is selected using field GSMODE of the GSADDINC command. Only one picture can be stored in the Display RAM. The range of the address pointers is 00h to 7Fh for X and 00h to 47h for Y. One byte loaded in the Display RAM contains data for one pixel.

In this mode, column outputs  $C_{n+1}$  and  $C_n$ , must be connected together. It is not possible to use the "two" color mode, see Section 9.1: Color Selection Modes for details. For more information on using this mode, refer to the description of command GSADDINC in Section 13.2.

X => Col1 Col126 Col127 Col128 Col2 - - -Row 1 PxI 0 Pxl 1 Pxl 125 Pxl 126 Pxl 127 Row 2 - - -Row 3 \_ \_ \_ Display Screen **Row 71 Row 72** Y 00h, X 00h Y 00h, X 01h Y 00h, X 7Dh Y 00h, X 7Eh Y 00h, X 7Fh Pxl 125 Pxl 127 PxI 0 Pxl 1 Pxl 126 Y 00h, X 00h Display RAM Y 46h X 00h Y 47h, X 00h Y 47h, X 7Fh Col 1\* Col 2\* Col 3\* Col 127\* Col 128\* Row 1 Pixel 0 Pixel 1 Pixel 2 Pixel 126 Pixel 127 b5---b0, Byte 01h b5---b0, Byte 00h b5---b0, Byte 02h b5---b0, Byte 7Eh b5---b0, Byte 7Fh Column to Pixel Mapping \* Default column mapping 128 columns, 72 rows

Figure 17: 64 Level Gray Scale Mode 1 - Display RAM Organization

Display RAM STV8105

## 3.4 64 Level Gray Scale Mode 2 Memory Map

In this mode, the picture has 256 x 36pixels, the gray scale of each pixel is defined by the corresponding 6-bit value stored in Display RAM. This mode is selected using field GSMODE of the GSADDINC command. Only one picture can be stored in the Display RAM. The range of the address pointers is 00h to FFh for X, 00h to 23h for Y. One byte loaded in the Display RAM contains data for one pixel.

The "two" color mode cannot be used, see Section 9.1: Color Selection Modes for detail. For more information on using this mode, refer to the description of command GSADDINC in Section 13.2.

X => Col1 Col2 Col254 Col255 Col256 Row 1 PxI 0 Pxl 1 - - -Pxl 253 Pxl 254 Pxl 255 Row 2 - - -Row 3 - - -Display Screen Row 35 - - -Row 36 Y 00h, X FDh Y 00h, X FEh Y 00h, X 00h Y 00h, X 01h Y 00h, X FFh Pxl 0 Pxl 1 Pxl 253 Pxl 255 Pxl 254 Y 00h, X 00h Display RAM Y 22h, X 00h Y 23h, X 00h Y 47h, X FFh Col 1\* Col 2\* Col 3\* Col 256\* Col 255\* Row 1 Pixel 0 Pixel 1 Pixel 2 Pixel 254 Pixel 255 b5---b0, Byte 00h b5---b0, Byte 01h b5---b0, Byte 02h b5---b0, Byte FEh b5---b0, Byte FFh Column to Pixel Mapping \* Default column mapping 256 columns, 36 rows

Figure 18: 64 Level Gray Scale Mode 2 - Display RAM Organization

STV8105 Display RAM

## 3.5 Monochrome Mode Memory Map

In this mode, the picture has 256 x 72 pixels, and each pixel is black or white depending on the corresponding 1-bit value stored in Display RAM. This mode is selected using field GSMODE of the GSADDINC command. Four pictures can be stored in the Display RAM. The "two" color mode can be used, see Section 9.1: Color Selection Modes for details. The range of the address pointers is 00h to 3Fh for X, 00h to 8Fh for Y. One byte loaded in Display RAM contains data for eight pixels. See Section 13.2.

Display RAM STV8105

Figure 19: Monochrome Mode - Display RAM Organization

STV8105 Display RAM

#### 3.6 Display RAM Loading

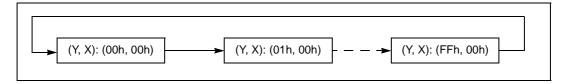

Four increment modes can be selected using the XINC and YINC bit of the GSADDINC command as described below:

- If bits YINC and XINC of command GSADDINC are both "Low", there is no increment of the X and Y Display RAM addresses.

- If YINC="High" and XINC="Low", then only the Y address of the Display RAM is incremented as shown is Figure 20.

Figure 20: Automatic Increment of Display RAM Y Address

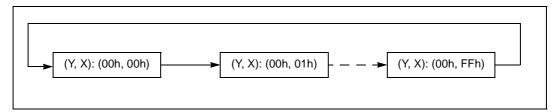

Conversely, if YINC="Low" and XINC="High", then only the X address of the Display RAM is incremented, Figure 21.

Figure 21: Automatic Increment of Display RAM X Address

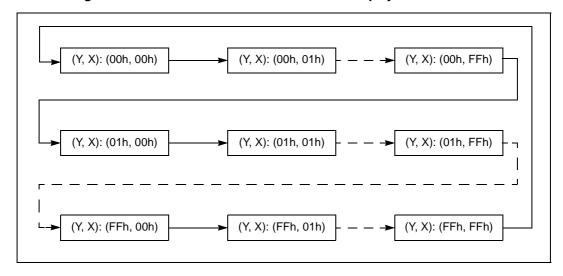

• If YINC and XINC are both "High", then both the X and Y addresses of the Display RAM are incremented. If the X address reaches its limit of FFh, then only Y address will be incremented, Figure 22.

Figure 22: Automatic Increment Both X and Y Display RAM Addresses

It is the software designer's responsibility to keep the X and Y address pointers consistent with the selected display mode by mainly using automatic incrementation to avoid writing data in areas that are not read.

Dot-Matrix Display STV8105

# 4 Dot-Matrix Display

The STV8105 can display pictures of different resolutions with different shades or levels of gray as described below:

16 level grayscale mode:  $256 \times 72 \times 4$  bits 4 level grayscale mode:  $256 \times 72 \times 2$  bits 64 level grayscale mode 1:  $128 \times 72 \times 6$  bits 64 levels grayscale mode 2:  $256 \times 36 \times 6$  bits

Black and White, monochrome mode:  $256 \times 72 \times 1$  bit

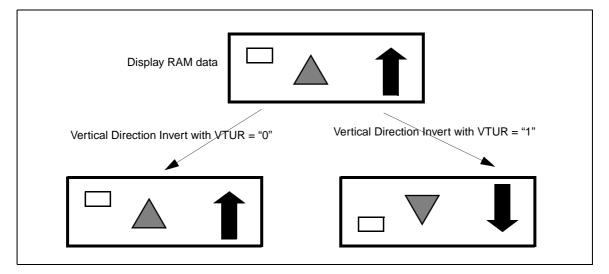

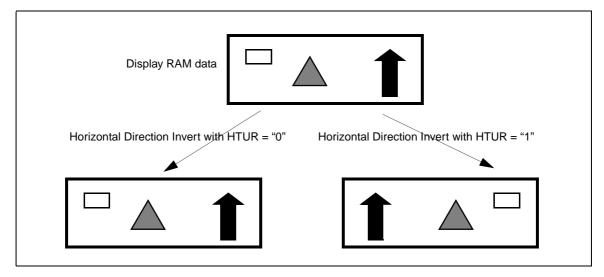

The selected picture in Display RAM can be displayed in four different ways thanks to bits VTUR and HTUR of the command DOTMTRXDIR (command code 11h):

- bit VTUR selects the vertical display direction versus Display RAM contents, Figure 23.

- bit HTUR selects the horizontal display direction versus Display RAM contents, Figure 24. Bit HTUR applies when writing data into the Display RAM. To get effective horizontal picture mirroring after changing the HTUR bit, the picture must be re-written into Display RAM.

The display is turned on when bit DISPON of command DCTRL (10h) is set; bit DISPON is cleared by default on reset or during power-on reset.

Figure 23: Invert Image - Vertical Direction

STV8105 Dot-Matrix Display

Figure 24: Invert Image - Horizontal Direction

The STV8105 can scan a reduced number of rows by programming the SCLN bit-field of command DOTMTRXSCAN (12h). See Section 13.2 for details regarding commands DCTRL, DOTMTRXDIR and DOTMTRXSCAN.

Clock Generation STV8105

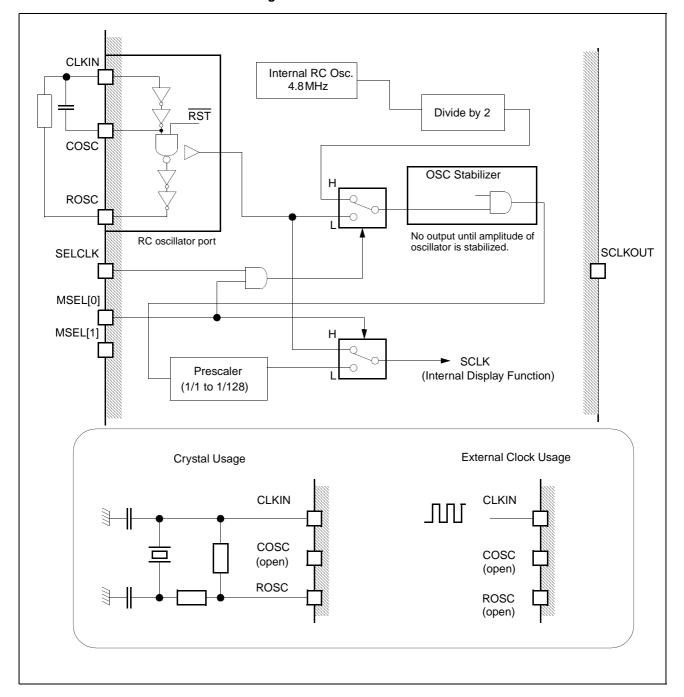

## 5 Clock Generation

The STV8105 has two on-chip oscillator circuits to generate the internal clock SCLK. One circuit is dedicated to an external crystal or RC network. It is also possible to source an external clock on pad CLKIN directly. A second RC oscillator is fully integrated. It does not require any external components and provides a reference clock of 4.8MHz, typ. The clock source is selected using input pads SELCLK and MSEL[0].

The internal clock SCLK is buffered and sent to output pad SCLKOUT for slave devices.

The oscillator frequency can be divided by a factor of 2<sup>N</sup>, where integer N can range from 0 to 7, by programming the SDIV bit-field of command SCLKDIV. This sets up a "prescaler" ratio of from 1/1 to 1/128; see Figure 25. For details regarding the SCLKDIV command, see Section 13.2: Command Details Ordered by Command Code.

STV8105 Clock Generation

Figure 25: Clock Generation

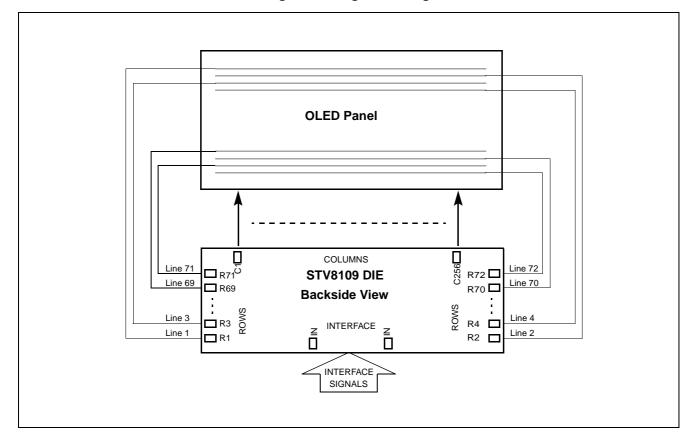

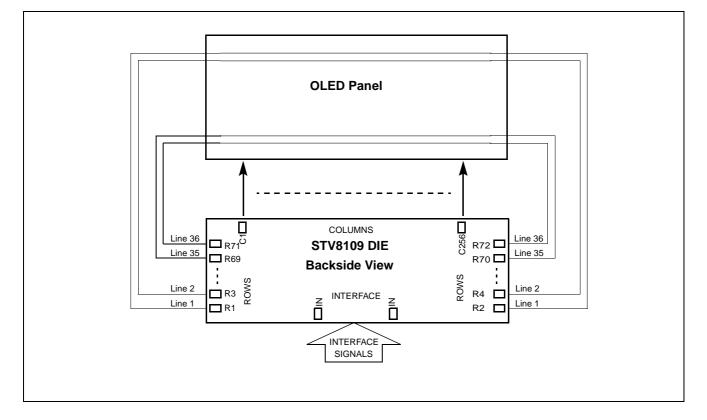

# 6 Master/Slave and Primary/Secondary Operation

Master/Slave operation of two STV8105s allows driving a panel of 512 columns by 72 rows with 16 levels of gray.

Master/Slave plus Primary/Secondary operation of four STV8105s (two along the top of the panel and two along the bottom, see Figure 26), allows driving 512 columns by 144 rows with 16 levels of gray.

The STV8105 sets up Primary/Secondary and Master/Slave assignments depending on the state of input pads MSEL[0] and MSEL[1] as described in Table 10.

Table 10: Master/Slave Operation

| MSEL[1] | MSEL[0] | Test Mode                                                                                                                                                                                                                                     |  |  |

|---------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| L       | L       | Secondary Slave (SS) Interface signals from the Secondary Master are received by the Secondary Slave. The Secondary Slave operates synchronously with Secondary Master.                                                                       |  |  |

| L       | Н       | Secondary Master (SM) Interface signals from the Primary Master are received by the Secondary Master. A output synchronizing signal is sent to the Secondary Slave.                                                                           |  |  |

| н       | L       | Primary Slave (PS) Interface signals from the Primary Master are received by the Primary Slave. The Primary Slave operates synchronously with Primary Master.                                                                                 |  |  |

| н       |         | Primary Master (PM) Interface signals of VSYNCOUT, HSYNCOUT, SD/COUT, etc. are activated Operation of the Primary Slave and Secondary Master are synchronous with the Primary Master. Row Driver Control signals RCTRLA/RCTRLB are activated. |  |  |

Primary Master and Secondary Master operate by CS1.

Primary Slave and Secondary Slave operate by  $\overline{\text{CS2}}$ .

512 columns by 72 rows two color display, 4-bit gray scale 2 column drivers 1 row driver Primary Master/Slave operation PM PS STV81 ST 8105 SM SS 512 columns by 144 rows two color display, 4-bit gray scale 4 column drivers 2 row drivers Primary Master/Slave and Secondary Master/Slave operation PM PS

Figure 26: Master/Slave and Primary/Secondary Operation

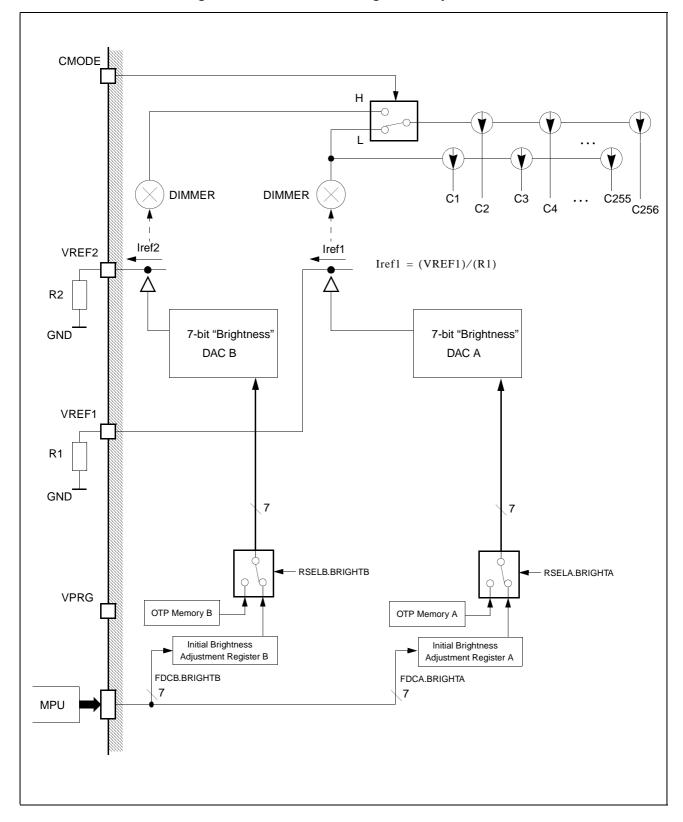

# 7 Brightness Adjustment

In the STV8105, a brightness (luminance) adjustment changes the current of the column drivers. The column current is a copy of a reference current which is defined by the ratio of a reference voltage on pad VREFx to the value of a precision resistor connected between pad VREFx and ground.

This reference voltage can range from 0.64 to 2.77 V. Using a 20 K precision resistor, for example, leads to a reference current of from 32 to 138.5  $\mu$ A. The maximum possible value of this reference current is 400 $\mu$ A; it can be set with either (VREF)/(Rfef) = (0.64V)/(0.6K) or (VREF)/(Rref) = (2.77V)/(6.925K).

The reference voltage is generated by an internal 7-bit DAC.

Input data to this DAC can come from an "initial brightness adjustment" register which is loaded by a BRIGHTx command or from data stored in an on-chip, one-time-programmable, non-volatile memory (Anti-Fuse OTP Memory). Input data to the DAC is selected with bit RSELx of command BRIGHTx. By default, the contents of OTP memory are selected as input to the DAC.

However, if the OTP memory is not already programmed, Section 11.2, the DAC will output an "undetermined" value between the minimum and the maximum possible for VREF. In this case, it is mandatory to program the DAC using the BRIGHTx command.

To support displays using "two" color pixels, the STV8105 has two independent brightness adjustments. Using bits RESLA and RSELB of commands BRIGHTA and BRIGHTB, DAC A and DAC B are loaded, respectively, with the contents of initial "brightness" registers A and B, or with the contents of two on-chip non-volatile memories A and B (Anti-Fuse OTP Memory), as shown in Figure 27.

See Section 13.2 regarding programming "brightness" register A using command BRIGHTA and "brightness" register B with command BRIGHTB.

As shown in Figure 27, the overall brightness of the display can also be adjusted by a dimmer control function - with the command DIMMERCTRL. For details regarding this function, refer to Section 9.2: Dimmer Control.

Figure 27: Control of Initial Brightness Adjustments

# 8 DC/DC Step-up Converter with VF Detection

# 8.1 General Description

The STV8105 contains a DC/DC converter controller capable of driving an external, 150mA, switching power MOS transistor with 90% efficiency. With just few external components a step-up converter can be realized capable of generating up to 25V from a 3 to 12V battery. The switching frequency can be set in the range of 150 to 300KHz which allows reducing inductor size. Normal protections such as under voltage lock-out (UVLO), detection against open loop operation and current overload are also included.

In general, a step-up converter design based on the DC/DC power controller of the STV8105 is capable of:

- operating from a 3 to 12V battery

- operating from a gate buffer supply (VDC) of 3 to 10V

- producing an adjustable output, V<sub>H</sub>, ranging from 6 to 25V

- sourcing up to 150mA at 18V

- requiring only 10µA in standby

- operating at efficiencies of up to 90%

- operating at switching frequencies of 100, 200, 250 and 300KHz

- protecting against overload, under voltage or open loop conditions

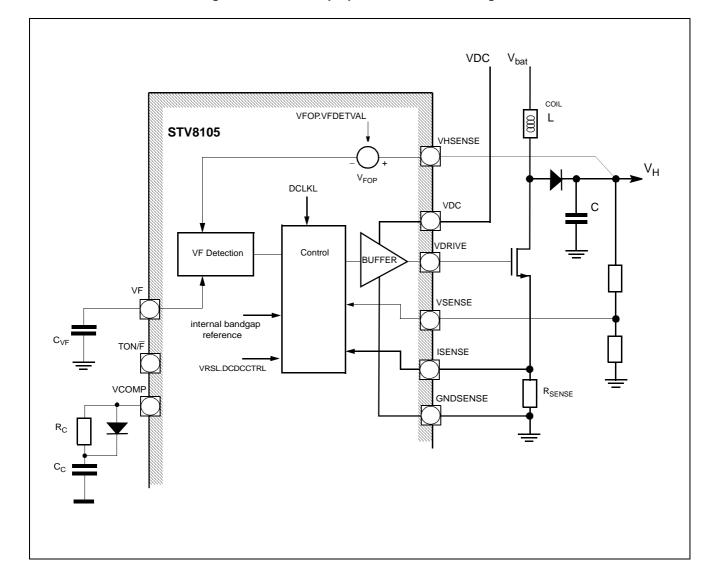

A block diagram of the converter is shown in Figure 28. The output of the converter is  $V_H$ . This output can be used to supply the row drivers with VROW1/VROW2 and the column drivers with VPP1/VPP2 and VCOL1/VCOL2.

The VF detection feature of the DC/DC controller monitors the voltage on column outputs C1 and C256 during constant current drive and stores an average of the two voltages on a capacitor connected to pad VF, see  $C_{VF}$  in Figure 28. This "detected" voltage is sampled and used by the control block in determining  $V_H$ . In addition, the VFOP bit-field of command VFDETVAL can be used to program a 3-bit DAC to output an adjustment to  $V_H$  according to

$$V_{H} = VF + V_{FOP}$$

where  $V_{FOP}$  can range from 1.5 to 3.5 V and one LSB = 286 mV.

Figure 28: DC/DC Step-up Converter - Block Diagram

Output  $V_H$  is "clamped" to  $V_H$  Max. which equals a constant  $\times$  VBG at the time of VF detection. If  $V_H$  Max. is exceeded, then pad RCTRLB is pulled "High" to VDD by the STV8105 indicating a voltage fault.

# 8.2 Detailed Description

The converter combines the advantages of two control schemes, pulse width modulation (PWM) or constant switching frequency mode and pulse frequency modulation (PFM) also called constant  $t_{ON}$  mode, which together provide high efficiency over a wide range of output load current. Selection between the two modes is done with pad  $TON/\overline{F}$ .

Output  $V_H$  can be adjusted from 6 to 25 V by means of two independent closed loops; one is through the VSENSE pad, the other through VHSENSE. The VSENSE-loop is enabled during power-on where  $V_H$  increases in proportion to the ramp-up characteristics of an internal bandgap source. The VHSENSE-loop is enabled when  $V_H$  is determined to have reached steady-state. Here,  $V_H$  tracks the voltage present on pad VF.

The DC/DC power controller also includes several protections designed to prevent damage to the STV8105 or external components. Under voltage lock-out (UVLO) shuts the gate drive buffer down if VDC becomes too low. The power-off threshold is 2.54V; the power-on threshold, 2.77V. VDC is internally filtered by the STV8105 so that the power controller does not react to glitches that might be present on this supply.

Over current protection on pad ISENSE senses the source current of the external switching MOS transistor and disables the gate drive buffer if this current exceeds 250mV/R<sub>SENSE</sub>. If this condition persists for 16 "internal" cycles, the buffer remains off until either VDC is removed or a reset such as pad RST going "Low" occurs.

Detection of an open-loop condition, either on VSENSE or VHSENSE, causes the STV8105 to also shut down the gate drive buffer. If an open-loop condition occurs with VHSENSE, then  $V_H$  rises to a value fixed by the external feedback resistor divider.

#### 8.2.1 PWM Mode

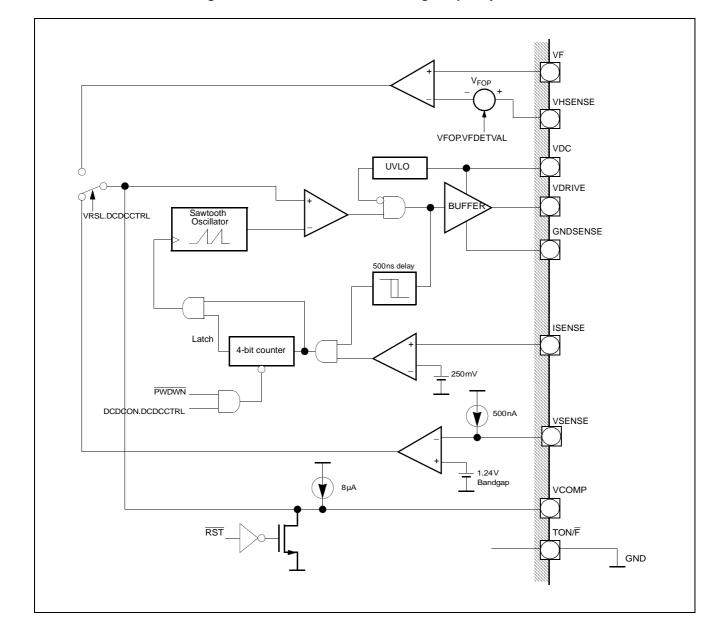

When pad  $TON/\overline{F}$  is connected "Low" to GND, the DC/DC converter operates in PWM or constant switching frequency mode.

The PWM circuit consists of a fixed frequency sawtooth generator, an error amplifier and a PWM comparator. The frequency of the generator can range from 150 to 300 KHz. The default is 150 KHz; the other values are programmed, see Section 13.2, with field FDCDC of command DCDCCTRL. Referring to Figure 29, the error amplifier is a transconductance operational amplifier (OTA) that compares an internal bandgap voltage with the voltage on pad VSENSE. The output of the OTA, pad VCOMP, is available for frequency compensation. The feedback signal on VSENSE is obtained using an external resister divider across the converter output  $V_{\rm H}$ .

The output of the error amplifier, VCOMP, is compared with the sawtooth waveform. If it is greater, the external switching MOS transistor is kept ON. If it is less, the MOS transistor is switched OFF.

Suppose  $V_H$  exceeds its steady state value by a small amount, then the output of the error amplifier goes "Low" causing the duty cycle to decrease. As a consequence  $V_H$  decreases. Thus the feedback is negative and can maintain  $V_H$  at its desired value.

Figure 29: PWM or Constant Switching Frequency Mode

### 8.2.2 PFM Mode

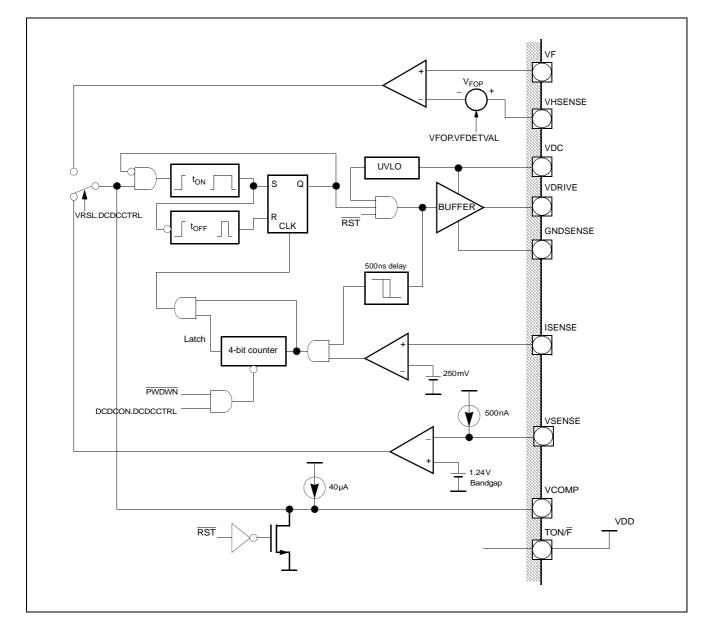

When pad  $TON/\overline{F}$  is connected "High" to VDD, the DC/DC converter operates in PFM or constant  $t_{ON}$  mode.

Referring to Figure 30, the PFM circuit consists of a  $t_{ON}/t_{OFF}$  oscillator that can be locked in the  $t_{OFF}$  state by the output of the VSENSE error amplifier. During  $t_{ON}$  the external MOS transistor is kept ON. It is switched OFF when a current limit or a  $t_{OFF}$  period occurs.

If output  $V_H$  becomes less than its steady state value, the output of the error amplifier remains "High" and a  $t_{ON}/t_{OFF}$  period starts. The external MOS transistor is switched ON and OFF, repeatedly, until  $V_H$  exceeds the steady state value. Then the output of the error amp goes "Low", and the clock is disabled. If a current limit is detected during a  $t_{ON}$  period, the oscillator is locked OFF until a another  $t_{ON}$  occurs. In this way, the switching frequency is varied until regulation is obtained.

In PFM mode the switching frequency scales roughly in proportion to the load current. Thus, this mode of operation enables high efficiency with light loads and is ideal to control the converter in standby mode. The PFM control technique does not need any frequency compensation. It is inherently stable.

Figure 30: PFM or Constant toN Mode

# 8.3 Compensation Network

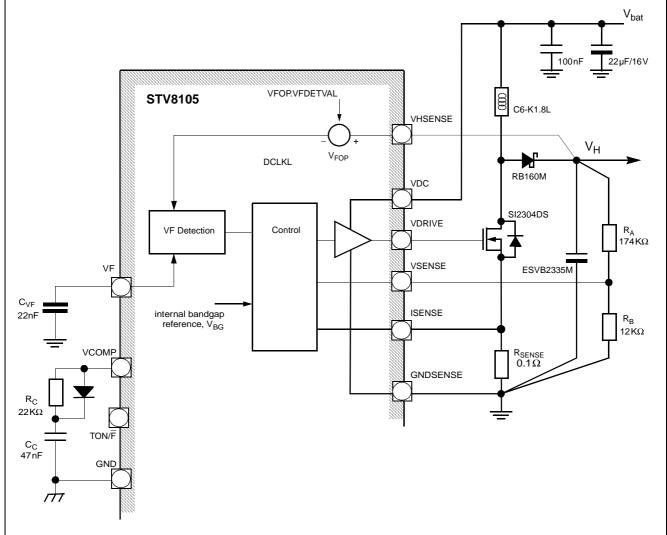

The LC output filter in Figure 28 has a two-pole transfer function. So to guarantee stability in PWM mode, it is necessary to frequency compensate the closed loop response of the converter.

The error amplifier plays a fundamental role in regulating the loop of the converter. This amplifier is an operational transconductance amplifier (OTA). Since the output of an OTA is high impedance, it is easy to compensate the converter by connecting an RC network between this node and ground. Thus the output of the OTA is bought out to a pad, VCOMP, where an external RC can be connected between it and ground, GND. See  $R_C$  and  $C_C$  in Figure 31 below.

The external RC introduces a dominant low-frequency pole in the response of the control loop. It also introduces a zero that can be placed to cancel the pole of the LC output filter.

Operation in PFM mode does not require frequency compensation.

Figure 31: DC/DC Converter - Application Circuit

#### 8.4 **Soft Start**

Soft start is an essential feature for correct power-up of the DC/DC converter without overstressing the external switching MOS transistor. Soft start operates during start up of the converter when bit DCDCON of command DCDCCTRL becomes "1". The soft start function is realized with the same capacitor, C<sub>C</sub>, that is used for frequency compensation. The soft start ramp-up time can be calculated by simply taking into account the output sourcing current of the OTA which is 40 µA in PWM mode and 8µA in PFM.

During power-up, the external MOS transistor starts switching with a duty cycle that gradually increases at the same rate as the voltage on pad VCOMP. In PFM mode, pad VCOMP is used only for soft start, and the voltage on this pad ramps-up to VDD.

### 8.5 Peak Current Detection

The drain-source voltage of the external switching MOS transistor is sensed by R<sub>SENSE</sub>, Figure 31, and as soon as a comparator detects that this voltage has exceeded 250 mV, the gate drive of the external MOS transistor is switched OFF.

When the comparator senses an over-current condition, a flip-flop is set, and the external MOS transistor is switched OFF. The flip-flop remains set while the over-current condition persists. If this condition persists for 16 continuous "internal" cycles, a master latch turns the DC/DC converter off, and the converter can not be restarted with DCDCON.DCDCCTRL = "1" until after a new power-up or hardware reset (RST = "0") is issued.

An internal low-pass filter in series with pad ISENSE with an inherent delay of 500ns rejects voltage glitches caused by the external switching MOS transistor during its operation.

Refer to Section 13.2: Command Details Ordered by Command Code for details regarding registers DCDCCTRL and VFDETVAL which control operation of the DC/DC converter.

STV8105 Column Drivers

# 9 Column Drivers

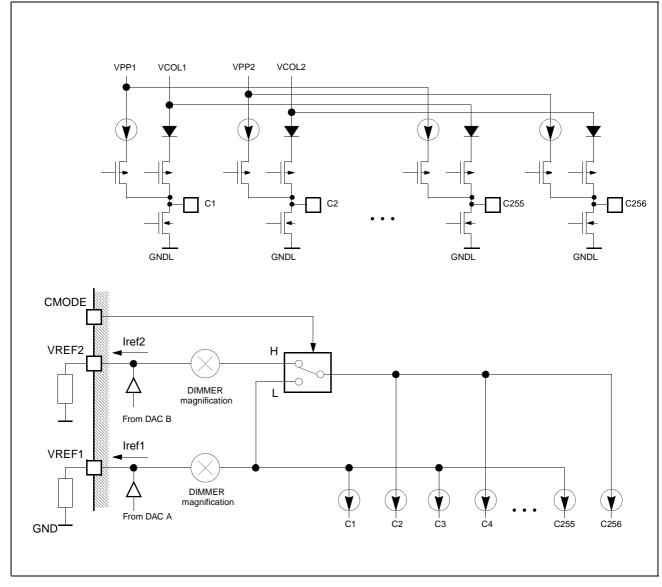

The column drivers of STV8105 are described in Figure 32.

Together, the column driver outputs C1 to C256 can be connected to three different sources or placed in Hi-Z. The three different source types are: a constant current supplied on pads  $VPP_X$ , a constant voltage supplied on pads  $VCOL_X$ , or switched to GNDL.

Supply pads VPP1 and VCOL1 are for the odd numbered outputs.

Supply pads VPP2 and VCOL2 are for the even numbered outputs.

The GNDL pad is common to all columns pads.

A dedicated command register (COLCTRL 1Ah) provides 4 control bits to override the column output signals:

- the CLLM bit, when set to "1" (with CLLZ = "0"), forces all column outputs to VCOL1 and VCOL2. It overrides all other column commands. The inactive default value is "0".

- bit CLLZ, when set, forces all column outputs in Hi-Z state and overrides all other commands. Inactive default value is "0".

- bit HSLZ, when set, forces output HSYNCOUT to Hi-Z. HSYNCOUT is grounded to pad GNDL when HSLZ is "0", the inactive default value.

- bit OFLZ, when set (with CLLM and CLLZ = "0" and after the PWM current sourcing period), forces all column outputs to Hi-Z, otherwise the outputs are grounded to GNDL when OFLZ is "0", the inactive default value.

### 9.1 Color Selection Modes

The STV8105 can drive dual or "two" color displays: one color appears on the odd columns, the other on even columns. Supplies VPPx and VCOLx as well as the column current generators can be set to different levels to fit the driving characteristics of the two colors. Two reference currents are defined by the selected "brightness" DAC (DAC A or DAC B) and by two precision resistors connected on pads VREF1 and VREF2. These resistors can have the same or different values. The dual current reference mode is selected by pulling pad CMODE "High" to VDD.

#### Note:

- In the dual color mode, the same dimmer control applies to the two colors.

- When using the 64 level gray scale modes (resolutions of 128 × 72 and 256 × 36), the dual mode cannot be used, supplies VPP1 and VPP2 as well as VCOL1 and VCOL2 must be connected together, and only DAC A (VREF1) can be used.

- When pad CMODE is pulled "Low" to GND, only one current reference is used. It is defined by the resistor on pad VREF1 and controlled by DAC A along with the dimmer command. See Figure 32.

Column Drivers STV8105

Figure 32: Column Drivers

Bit HTUR of the command DOTMTRXDIR can be used to reverse the horizontal display direction versus column pinout. Note that the picture must be reloaded because HTUR can only change the Display RAM write direction. Refer to Section 13.2 for details.

### 9.2 Dimmer Control

The brightness of the whole display panel can be changed with the DIMM bit-field of command DIMMERCTRL. DIMM selects what fraction of  $I_{ref}$  to use in establishing the column output current  $I_{COUT}$  which is given by

$$I_{COUT} = Iref \times fract[DIMM]$$

where fract[DIMM] is a fraction depending on the value of field DIMM according to Table 11 below. For more info on command DIMMERCTRL see Section 13.2.

STV8105 Column Drivers

**Table 11: Dimmer command**

| DIMM.DIMMERCTRL | fract[DIMM] | Ratio of Iref [%] |

|-----------------|-------------|-------------------|

| b4 b3 b2 b1 b0  |             |                   |

| 0 0000          | 1/16        | 6.25              |

| 0 0001          | 2/16        | 12.5              |

|                 |             |                   |

| 0 0011          | 4/16        | 25                |

|                 |             |                   |

| 0 0111          | 8/16        | 50                |

|                 |             |                   |

| 0 1011          | 12/16       | 75                |

|                 |             |                   |

| 0 1111          | 16/16       | 100               |

|                 |             |                   |

| 1 0011          | 20/16       | 125               |

|                 |             |                   |

| 1 0111          | 24/16       | 150               |

|                 |             |                   |

| 1 1011          | 28/16       | 175               |

|                 |             |                   |

| 1 1111          | 32/16       | 200               |

Note: Note: A "Dimmer" adjustment is performed synchronous with VSYNC when bit DISPON of register DCTRL is "1". Otherwise, when DISPON.DCTRL is "0", this adjustment is performed immediately after the command DIMMERCTRL is issued.

### 9.3 Drive Control

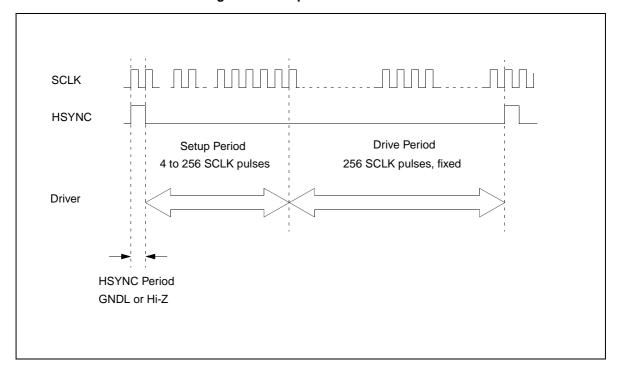

The STV8105 outputs a constant current on each column pad depending on the "Brightness" and "Dimmer" levels selected by the user. During the row period, the column current is PWM modulated according to the gray scale value of each pixel. A row (or scan line) period is divided into an OLED Setup Period for reset and precharge followed by a Drive Period (constant current gradation display).

Column Drivers STV8105

Figure 33: Setup and Drive Periods

# 9.4 Setup Period

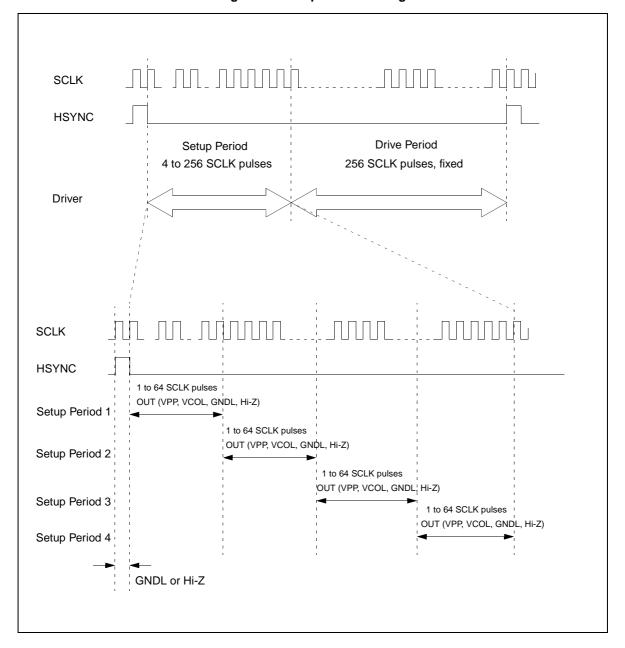

The Setup Period is composed of four programmable sub-periods. Each sub-period is programmed using a corresponding OELPERIOD1, 2, 3 or 4 (1Bh, 1Ch, 1Dh or 1Eh) command.

The duration of each sub-period can be programmed to be 1 to 64 SCLK clock periods long using the ExCL bit-field of the corresponding OELPERIODx command, x = 1, 2, 3 or 4. This leads to a total Setup Period of between 4 and 256 SCLK clock periods as shown in Figure 34.

The column output signal of a column pad can be programmed independently during the four subperiods using the ExST bit-field of the corresponding OELPERIODx command, x = 1, 2, 3 or 4, as explained below. The selected column driver output can:

- 1. source a constant current determined by the brightness and dimmer adjustments, Figure 32,

- 2. be forced to VCOLx,

- 3. be pulled down to ground GNDL or

- 4. be placed in a Hi-Z state.

If the pixel value to be displayed is 00h (i.e., black), then independent of whether the selected column output is programmed to be at VPPx, VCOLx or in Hi-Z during the setup period, the column output is pulled down to ground GNDL during the whole of the setup period and during the whole of the drive period as well.

Note: before the first setup period, 1 SCLK clock period is inserted in a row period sequence. During this time, the output HSYNCOUT can be pulled to ground GNDL or put in Hi-Z using bit OFLZ of the command COLCTRL (1Ah).

STV8105 Column Drivers

Figure 34: Setup Period Timing

## 9.5 Drive Period

The active duration of a row period (or scan line period) is named the drive period. The drive period is 256 SCLK clock periods long.

During the drive period, the column drivers are sourcing constant current defined by the brightness and dimmer levels selected by the user. The time the column current is sourced is proportional to the gray scale level of the pixel to be displayed, leading to a PWM modulation. This "sourcing" time can have 256 different values. After the "sourcing" time elapses, column current is turned off, and the column pad is switched to ground GNDL until the next setup period.

The STV8105 has a 30 byte lookup table to define the current sourcing duration of the drive sequence.

Column Drivers STV8105

There are 15 bytes dedicated to the odd columns and 15 bytes dedicated to the even columns. They can be loaded thanks to dedicated ODDx and EVENx commands (command codes 2Dh to 1Fh and 3Ch to 2Eh).

Separate ODDx and EVENx lookup tables can be used in case of "two" color modes. For a given level of gray, the odd and even bytes can be loaded with different values to fit each color brightness response. The STV8105 uses ODD and EVEN (or ODD only) lookup tables depending on the input level at pad CMODE. When CMODE is "High", the ODD lookup table applies to the odd columns, and the EVEN lookup table applies to the even columns. When CMODE is "Low", only the ODDx lookup table is used for both even and odd columns.

For some gray scale modes the lookup tables are not user accessible; see next sections. For details regarding the ODDx and EVENx commands, refer to Section 13.2: Command Details Ordered by Command Code.

STV8105 Column Drivers

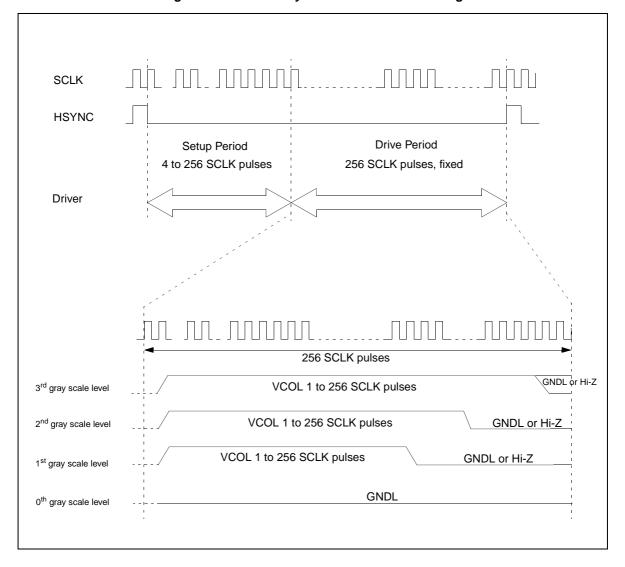

### 9.5.1 16 Level Gray Scale Mode

In this mode the gray level of each pixel is defined by a 4-bit value stored in the Display RAM, leading to 16 levels of gray.

**SCLK HSYNC Drive Period** Setup Period 4 to 256 SCLK pulses 256 SCLK pulses, fixed Driver 256 SCLK pulses GNDL or Hi-Z VCOL 1 to 256 SCLK pulses 15<sup>th</sup> gray scale level 14th gray scale level VCOL 1 to 256 SCLK pulses GNDL or Hi-Z VCOL 1 to 256 SCLK pulses GNDL or Hi-Z 13th gray scale level VCOL 1 to 256 SCLK pulses GNDL or Hi-Z 2<sup>nd</sup> gray scale level **VCOL** GNDL or Hi-Z 1st gray scale level **GNDL** 0<sup>th</sup> gray scale level

Figure 35: 16 Level Gray Scale Mode - Drive Timing

This mode uses the ODDx and EVENx, or ODDx only, lookup tables to define the column current sourcing time. There are 15 bytes corresponding to the 15 different, possible values of pixel data in Display RAM. When the pixel value is 0h, the column current source is off (to GNDL) for the entire drive period.

Each byte of the lookup table holds a value between 0 to 256 (00h to FFh). This value corresponds to the number of elementary SCLK clock periods. Each byte of the lookup table is loaded using the corresponding ODDx or EVENx command. These bytes must be loaded during the power-on/reset sequence.

Column Drivers STV8105

### 9.5.2 4 Level Gray Scale Mode

In this mode the gray level of each pixel is defined by a 2-bit value stored in the Display RAM, leading to 4 levels of gray.

Figure 36: 4 Level Gray Scale Mode - Drive Timing

Because only 4 gray levels are used in this mode, only 3 or 6 from among the 15 or 30 lookup tables are needed:

ODD3, ODD2, ODD1 and EVEN3, EVEN2, EVEN1 when pad CMODE is "High" and ODD3, ODD2, ODD1 when CMODE is "Low".

The lookup table bytes must be loaded during the power-on/reset sequence.

STV8105 Column Drivers

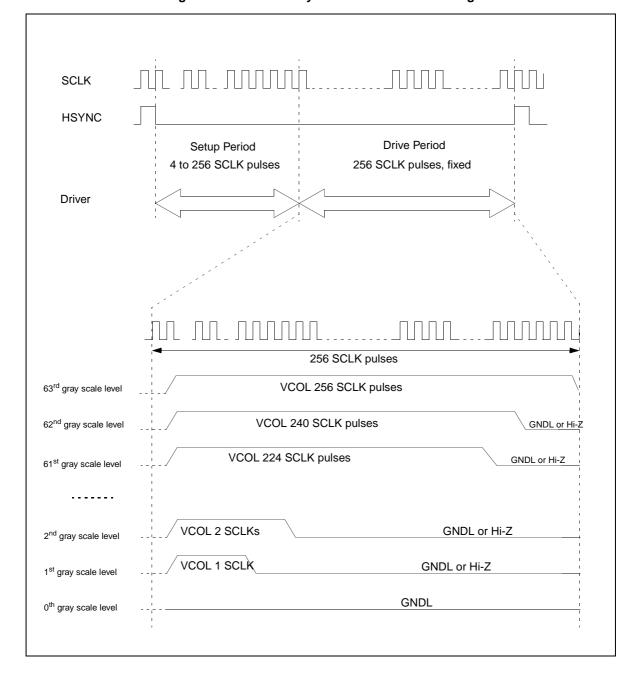

### 9.5.3 64 Level Gray Scale Mode

Figure 37: 64 Level Gray Scale Mode - Drive Timing

In this mode the lookup table is not user programmable. It is shown below in Table 12 which lists the number of SCLK clock pulses generated for each of the 64 possible values of a 6-bit pixel.

Column Drivers STV8105

Table 12: Lookup Table for 64 Level Gray Scale Mode

| Pixel value | Lookup byte           |

|-------------|-----------------------|

| binary      | number of SCLK pulses |

| 11 1111     | 256                   |

| 11 1110     | 240                   |

| 11 1101     | 224                   |

| 11 1100     | 208                   |

| 11 1011     | 200                   |

| 11 1010     | 192                   |

| 11 1001     | 184                   |

| 11 1000     | 176                   |

| 11 0111     | 168                   |

| 11 0110     | 160                   |

| 11 0101     | 152                   |

| 11 0100     | 144                   |

| 10 0011     | 136                   |

| 11 0010     | 128                   |

| 11 0001     | 120                   |

| 11 0000     | 112                   |

| 10 1111     | 108                   |

| 10 1110     | 104                   |

| 10 1101     | 100                   |

| 10 1100     | 96                    |

| 10 1011     | 92                    |

| 10 1010     | 88                    |

| 10 1001     | 84                    |

| 10 1000     | 80                    |

| 10 0111     | 76                    |

| 10 0110     | 72                    |

| 10 0101     | 68                    |

| 10 0100     | 64                    |

| 10 0011     | 60                    |

| 10 0010     | 56                    |

| 10 0001     | 52                    |

| 10 0000     | 48                    |

| 01 1111     | 46                    |

| Pixel value | Lookup byte           |

|-------------|-----------------------|

| binary      | number of SCLK pulses |

| 01 1110     | 44                    |

| 01 1101     | 42                    |

| 01 1100     | 40                    |

| 01 1011     | 38                    |

| 01 1010     | 36                    |

| 01 1001     | 34                    |

| 01 1000     | 32                    |

| 01 0111     | 30                    |

| 01 0110     | 28                    |

| 01 0101     | 26                    |

| 01 0100     | 24                    |

| 01 0011     | 22                    |

| 01 0010     | 20                    |

| 01 0001     | 18                    |

| 01 0000     | 16                    |

| 00 1111     | 15                    |

| 00 1110     | 14                    |

| 00 1101     | 13                    |

| 00 1100     | 12                    |

| 00 1011     | 11                    |

| 00 1010     | 10                    |

| 00 1001     | 9                     |

| 00 1000     | 8                     |

| 00 0111     | 7                     |

| 00 0110     | 6                     |

| 00 0101     | 5                     |

| 00 0100     | 4                     |

| 00 0011     | 3                     |

| 00 0010     | 2                     |

| 00 0001     | 1                     |

| 00 0000     | 0                     |

Note: odd and even columns have the same value, so there is NO "two" color mode in the 64 level gray scale modes.

STV8105 Column Drivers

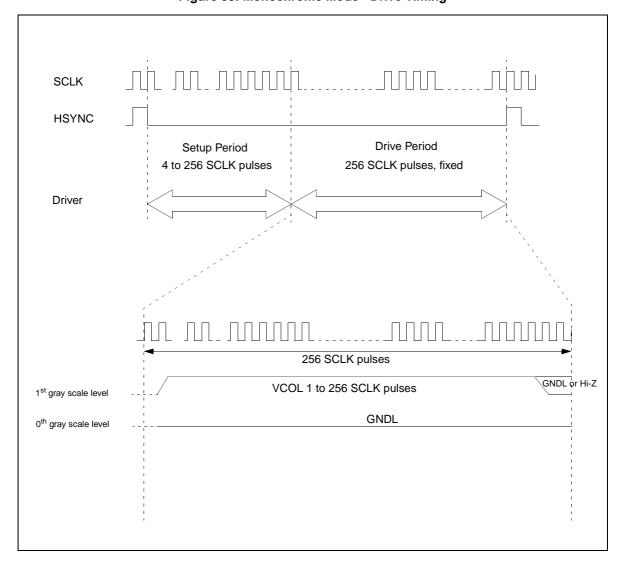

#### 9.5.4 Monochrome Mode

In this mode a pixel is ON or OFF depending on the value of the bit in Display RAM. The column current sourcing time is 0 when the pixel is OFF. It is equal, in terms of SCLK clock pulses, to the value of the byte loaded by the corresponding ODD1 or EVEN1 command (CMODE "High") or by the ODD1 command (CMODE "Low") when the pixel is ON. The lookup table byte(s) must be loaded during the power-on/reset sequence.

Figure 38: Monochrome Mode - Drive Timing

**Row Driver Control** STV8105

#### 10 **Row Driver Control**

#### 10.1 **Row Drivers**

The row driver of STV8105 is the 2-transistor structure shown below in Figure 39.

When activated, the row output pad is switched to GNDL. When not active, the row output pad is pulled-up to the voltage supplied on pads VROW1 and VROW2. The RON of the MOS transistor to GNDL is 10 ohms, max.

VROW1 VROW2 R2 R71 R72 R1

Figure 39: Row Drivers

Bit VTUR of command DOTMTRXDIR can be used to select the vertical display direction versus Display RAM contents. Refer to Section 13.2 for details.

The ROWDRVSEL command allows selecting the scanning direction as well as whether single or dual scanning mode is used.

#### 10.2 **Row Driver Scanning Modes**

### 10.2.1 Single Scanning Mode

The single scanning mode is selected when the RMODE bit-field of command ROWDRVSEL is programmed to "10b".

In single scanning mode when the RDIR bit of command ROWDRVSEL is "0", the Row Drivers are scanned in increasing order from R1 to R72.

When RDIR.ROWDRVSEL is "1", the rows are scanned in reverse order starting from R72.

STV8105 Row Driver Control

Figure 40: Single Scanning

### 10.2.2 Dual Scanning Mode

The dual scanning mode is selected when the RMODE bit-field of command ROWDRVSEL is programmed to "11b".

In dual scanning mode the odd and even row driver scans are simultaneous.

A maximum of 36 lines can be scanned at once, and the 2 row pads can sink with an effective  $R_{ON}$  of 5 ohms, max.

The scanning direction is changed, again, with bit RDIR of command ROWDRVSEL.

Row Driver Control STV8105

Figure 41: Dual Scanning

STV8105 OTP Memory

# 11 OTP Memory

#### 11.1 Introduction

The OTP (One Time Programmable) Memory consists of a Volatile Memory (VM) made of an array of flip-flops and a Non-Volatile Memory (NVM) made of an array of anti-fuses. Every time the STV8105 is powered-on or exits from reset, the OTP is automatically initialized. The NVM is powered on. Calibration and configuration parameters that are already stored in the NVM are read and latched into VM, then the NVM is powered off to avoid extra current consumption.

# 11.2 OTP Memory Programming

In order to store the calibration and configuration parameters permanently, the contents of VM has to be transferred to the NVM.

Below are details of the commands that allow permanently storing calibration and configuration data into the NVM.

| Comman | Function                                      | Addr |      | Command Data |      |      |      |      |      |             |         |  |  |  |

|--------|-----------------------------------------------|------|------|--------------|------|------|------|------|------|-------------|---------|--|--|--|

| d      | Function                                      | Addi | Bit7 | Bit6         | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0        | Default |  |  |  |

| SHORT  | VPRG internally<br>shorted to GNDL,<br>ON/OFF | F3   | 0    | 0            | 0    | 0    | 0    | 0    | 0    | SHORT<br>ON | 01h     |  |  |  |

| PRGOTP | OTP<br>Programming                            | F5   | 0    | 0            | 0    | 0    | 0    | 0    | 0    | 1           | -       |  |  |  |

| СКММ   | if SEAL bit = "1",<br>SW Reset, else<br>NOP   | F7   | -    | -            | -    | -    | -    | -    | -    | -           | -       |  |  |  |

First of all, care has to be taken when the programming voltage is applied to pad VPRG. Before powering-up VPRG, the internal switch between VPRG and ground (GND) has to be opened by making sure bit SHORTON of command SHORT is "0".

The OTP programming procedure is activated with the PRGOTP command. This procedure, which last about 50ms, autonomously involves blowing the anti-fuses. This procedure also terminates autonomously.

With the CKMM command it is possible to check if OTP memory has been correctly programmed. When CKMM is executed, the STV8105 checks the state of an internal "SEAL" bit. If this bit is "1", meaning the OTP memory has been correctly programmed, the STV8105 gets reset. If the "SEAL" bit is not "1", the CKMM command is ignored.

The recommended conditions for "blowing" and achieving a reliable short circuit of the anti-fuses are:

- Minimum programming current I<sub>PRG</sub> > 250 mA

- Programming voltage V<sub>PRG</sub> = 16V, accepted range 14V < V<sub>PRG</sub> < 18V</li>

- Time to program all cells Twr > 50 ms

OTP Memory STV8105

# 11.3 A Short Routine for Programming the OTP

Below, a short routine that can be used to program and check the OTP memory of the STV8105.

|            | # Power on VDD.                                             |

|------------|-------------------------------------------------------------|

| 01h        | # Issue BRIGHTA command, initial brightness "A" adjustment. |

| 00h to 7Fh | # Set desired default value for brightness "A".             |

| 02h        | # Issue BRIGHTB command, initial brightness "B" adjustment. |

| 00h to 7Fh | # Set desired default value for brightness "B".             |

| F3h        | # Issue SHORT command                                       |

| 00h        | # with Bit0 of next word, SHORTON, equal to "0",            |

|            | # i.e. short is off.                                        |

|            | # Now power on VPRG.                                        |

| F5h        | # Issue PRGOTP command                                      |

| 01h        | # with Bit0 of next word equal to "1".                      |

|            | # Wait 50ms.                                                |